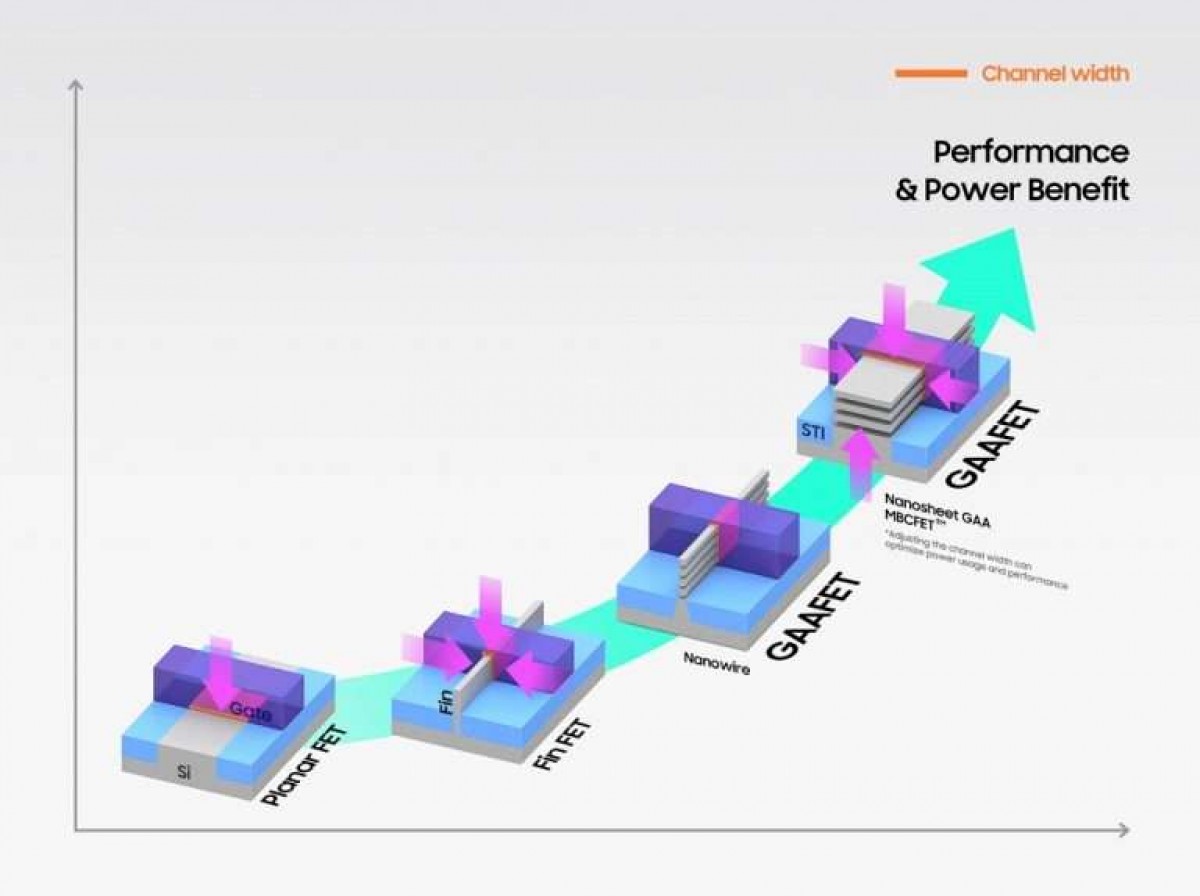

A Samsung Foundry anunciou que está iniciando a produção em massa de seus chips de primeira geração no nó de 3nm. É baseado na nova arquitetura de transistor GAA (Gate-All-Around), que é o próximo passo após o FinFET.

Em comparação com 5nm, os chips de 3nm de primeira geração da Samsung podem oferecer um desempenho até 23% melhor, até 45% de redução no consumo de energia e uma redução de 16% na área de superfície.

O nó de 3nm de segunda geração da Samsung será ainda mais impressionante – comparado aos 5nm, a Samsung afirma que alcançará uma redução de 50% no consumo de energia, até 30% de melhoria no desempenho e uma redução de 35% na área.

A Samsung está agora à frente da TSMC, que deve iniciar a produção em massa de chips de 3nm durante o segundo semestre do ano.

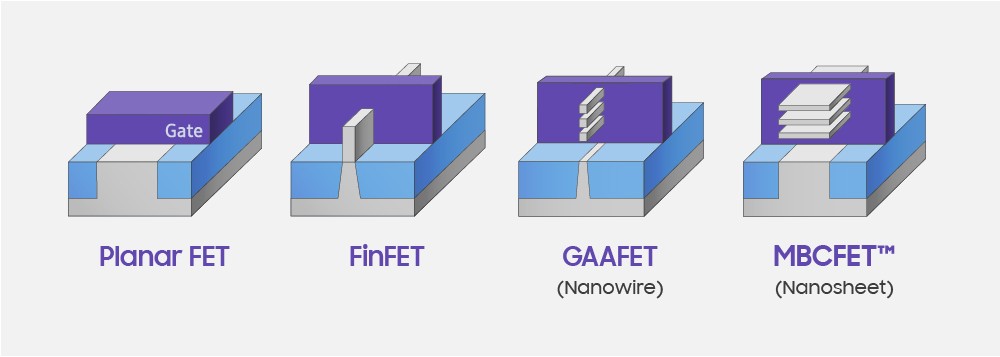

O design do transistor Gate-All-Around (GAA) permite que a fundição encolha os transistores, sem prejudicar sua capacidade de transportar corrente. O design GAAFET usado no nó de 3 nm é o MBCFET mostrado na imagem abaixo.

A evolução dos transistores de silício

A evolução dos transistores de silício

Via: GSMArena